The National Office of Intellectual Property (NOIP) has just granted a patent for the invention titled: “A method for evaluating the security level of hardware based on power estimation traces.” This is the result of research by the Smart Integrated Systems Laboratory (SISLAB) – Center for IC Design Research and Application, Information Technology Institute, Vietnam National University, Hanoi (VNU). The invention introduces an effective approach to evaluating the security of integrated circuit designs at the design stage, prior to manufacturing.

|

A Breakthrough Solution in Hardware Security Evaluation

The invention proposes a systematic technical process that enables the evaluation of the security level of cryptographic hardware designs during the design phase — by analyzing power consumption traces estimated through simulation, rather than waiting until the chip is physically manufactured.

Traditionally, hardware security testing is only conducted after the design has been fabricated into an integrated circuit using ASIC or FPGA technology, which is both costly and time-consuming. In the context of increasingly sophisticated side-channel attacks, early detection of information leakage points has become essential.

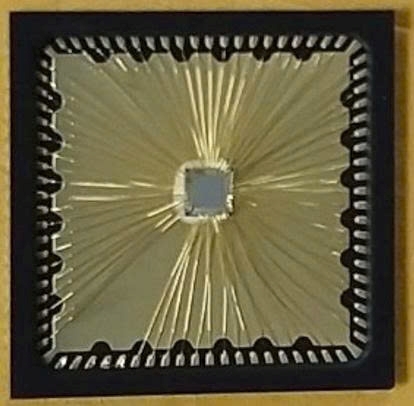

The patented process includes steps from design specification, RTL architectural description, functional simulation, hardware synthesis, timing and parasitic analysis, to power consumption estimation and security evaluation using statistical techniques such as T-test, Differential Power Analysis (DPA), and Correlation Power Analysis (CPA). The entire process is performed on the design model before fabrication, significantly reducing costs and enabling early detection of potential security vulnerabilities.

Practical Applications in High-Security IC Design

The invention is particularly useful in the design and evaluation of hardware encryption modules such as AES, RSA, and ECC, which serve high-security applications like banking cards, electronic ID cards, military systems, secure IoT devices, and trusted embedded systems.

For example, power side-channel attacks can recover an AES key in just a few minutes if the hardware design is not properly protected. This patented solution offers a powerful technical tool to validate and enhance resistance against secret key leakage in hardware designs.

|

A Significant Advancement in Integrated Circuit Design Research in Vietnam

The granting of a patent for this solution affirms the research and development capabilities of Vietnamese scientists in the fields of semiconductor integrated circuit design and information security — high-tech areas currently prioritized for investment and development by the Government.

It also serves as clear evidence of the effective integration of several key research directions, including hardware cryptography, side-channel security analysis, digital IC design (RTL/ASIC/FPGA), and pre-silicon security verification.

Patented Technical Process

The patented process for evaluating the security level of hardware based on estimated power traces includes the following steps:

(i) specifying the cryptographic/security design;

(ii) designing the hardware at the Register Transfer Level (RTL);

(iii) simulating and functionally verifying the design;

(iv) synthesizing and implementing the hardware design;

(v) extracting parasitic resistance and capacitance information, and performing static timing analysis to verify timing constraints;

(vi) simulating the design with parasitic data and extracting signal waveforms;

(vii) estimating power consumption and generating corresponding power traces;

(viii) interpolating and decomposing the power traces;

(ix) evaluating hardware security based on the collected traces;

(x) integrating the design into the system, ready for IC fabrication.